# FOPAC: Flexible On-chip Power and Clock

Ragh Kuttappa, Student Member, IEEE, Selçuk Köse, Member, IEEE, and Baris Taskin, Senior Member, IEEE

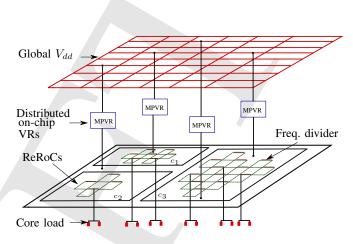

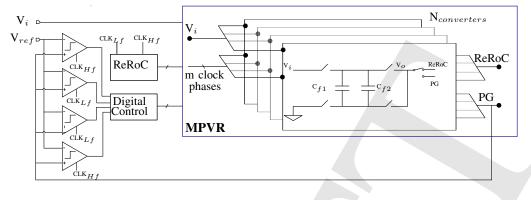

Abstract—A novel flexible on-chip power and clock (FOPAC) generation and distribution circuit is proposed to enable fast dynamic voltage and frequency scaling (DVFS). FOPAC utilizes resonant rotary clocks (ReRoCs) along with multi-phase voltage regulators (MPVR) for the clock and power generation and distribution. The locally distributed ReRoCs provide the required clock phases to the MPVR, and the MPVR provides the required voltage levels to the ReRoC, providing spatial and temporal flexibility for fast DVFS. The ReRoC and MPVR share the on-chip fly capacitor of the switched capacitor voltage regulators to achieve greater frequency scaling at run-time while reducing the overhead. The FOPAC architecture is evaluated on industrial designs demonstrating a <2 ns DVFS switching time.

Index Terms—Resonant rotary clock, voltage regulators, low power, VLSI.

# I. INTRODUCTION

**M** ODERN integrated circuits have an increasing need for various levels of both supply voltage (V) and operating frequency (f) available at fine spatial and temporal granularity. This work introduces a unique solution that provides a high number and quality of locally distributed V/f domains through FOPAC, as shown in Figure 1. Opportunistically sharing design resources and features between multi-phase voltage regulators (MPVRs) and resonant rotary clocks (ReRoCs) enabling i) the scalability to hundreds of domains, ii) fast switching times for both voltage and frequency, leading to temporal flexibility, and iii) locally distributed designs, leading to spatial flexibility.

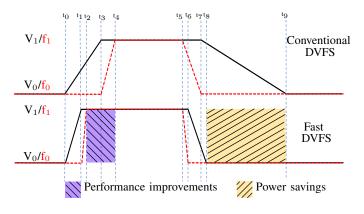

The performance improvements and power savings enabled by flexible on-chip power and clocks (FOPAC) are motivated in Figure 2 with shaded regions. When a higher performance is needed, the voltage is scaled up  $(V_0 \text{ to } V_1)$  followed by frequency up-scaling ( $f_0$  to  $f_1$ ). The speed of V/f up-scaling enables high performance node starting at time t<sub>2</sub> as opposed to  $t_4$  in Figure 2. Alternatively, when a lower performance is sufficient (i.e. for better energy-efficiency), the frequency is decreased followed by voltage down-scaling. Here, the speed of down-scaling enables higher amount of time to be spent in the lower performance node, initiated at time t<sub>8</sub> as opposed to t<sub>9</sub> in Figure 2. The granularities of the voltage V and frequency f values achievable with specific hardware implementations also impact the energy-efficiency. Costly implementations of fractional PLLs are used to provide frequency granularity (such as in [1]), whereas a multitude of voltage regulators and power grids are common to provide voltage granularity.

R. Kuttappa and B. Taskin are with the Department of Electrical and Computer Engineering, Drexel University, Philadelphia, PA 19104 USA (e-mail:ragh@drexel.edu; taskin@coe.drexel.edu). S. Köse is with the Department of Electrical and Computer Engineering, University of Rochester, Rochester, NY 14627 USA (e-mail: selcuk.kose@rochester.edu).

Fig. 1. FOPAC topology with resonant rotary clocks (ReRoC) and multiphase voltage regulators (MPVR).

FOPAC provides spatially and temporally flexible power/clock domains that are fine-tuned for each individual unit and collectively designed with shared overhead with superior performance. This flexibility comes with significant savings in power, performance, area, and accuracy, thanks to the opportunistic design of the MPVR and the ReRoC, leading to the following novelties:

- 1) fast switching between different V/f pairs,

- 2) symmetric switching between V/f pairs to improve power savings and performance, as illustrated in Figure 2,

- improved granularity of frequency values, without the overhead of multiple fractional PLLs distributed locally,

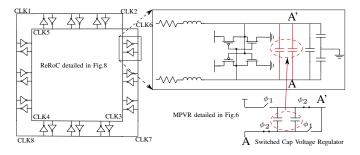

- 4) opportunistic sharing of the fly capacitor as illustrated in Figure 3, to reduce design overhead and to help scale

Fig. 2. Fast and symmetric DVFS with FOPAC.

Fig. 3. FOPAC circuit with the multiphase voltage regulator sharing the fly capacitor with the resonant rotary clock.

the ReRoC frequency,

5) power savings of  $\approx 35\%$  as compared to PLL based designs.

The preliminaries encapsulating the circuit level aspects necessary for the proposed DVFS approach with ReRoCs and MPVRs are presented in Section II. The proposed architecture is presented in Section III. The simulation setup and results are discussed in Section IV. Conclusions are provided in Section V.

#### **II. PRELIMINARIES**

The following sections discuss the on-chip voltage regulator and resonant rotary clock background, and prior works.

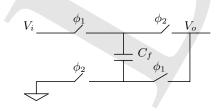

#### A. Switched Capacitor Voltage Regulator

On-chip voltage regulators (OCVRs) have been widely studied in prior works making the implementation feasible in traditional CMOS processes [2-5]. OCVRs can provide faster voltage scaling, reduce the number of dedicated I/O pins to the power, and facilitate fine granularity power management techniques [2, 4, 6]. Switched capacitor voltage regulators (SCVR) utilize fly capacitors to generate a DC output voltage [2]. A schematic of a 2:1 SCVR is illustrated in Figure 4. SCVRs are designed with non-overlapping signals  $\phi_1$  and  $\phi_2$  that operate at the MHz frequency range [7]. The intrinsic, switching, and conduction loses related to the fly capacitors result in lower conversion efficiency. To overcome the ripple at the output, multi-stage interleaving is proposed [3, 8]. Interleaving necessitates the need for multiple phases of the clock [3, 8]. To generate multiple clock phases, dedicated and robust clock sources are required.

Fig. 4. 2:1 Switched capacitor voltage regulator (SCVR).

CLK. CLK CLK CLK6 CLK CLK4 CLK: CLK: MOSAB MOSAB MOSAE MOSAE MOSAE MOSA Main-loop CLK1 <u>CLK3</u> CLK3 CLK CLK MISAB MISAB MISAB MISAB MISAB Sub-loop

Fig. 5. Dynamic resonant rotary frequency divider [11].

#### B. Resonant Rotary Clock Design

Resonant rotary clocks (ReRoCs) is a type of resonant clocking with constant magnitude, low power, low jitter, and multiple phases [9]. ReRoCs are designed using IC interconnects for the transmission lines and inverter pairs that are uniformly distributed along the transmission lines in antiparallel fashion, as illustrated in Figure 3. The ReRoC is modeled as an LC oscillator, where the frequency is estimated by,

$$f_{osc} = \frac{1}{2\sqrt{L_T C_T}}.$$

(1)

In Eq. (1),  $f_{osc}$  is the operating frequency of the ReRoC. The total inductance and total capacitance is given by  $L_T$  and  $C_T$ , respectively [9]. Most efficient design of ReRoCs are sparse rotary oscillator arrays (SROA) [10], similar to a non-uniform clock mesh topology. The capacitive load and inductance affect the frequency of oscillations. SROA is correct by design through algorithmic novelties proposed in the local distribution for use in the proposed FOPAC methodology.

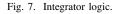

The improved granularity of frequency values, without the overhead of multiple local fractional PLLs, is achieved via the use of the resonant frequency dividers [11]. The frequency dividers, as illustrated in Figure 5, are designed with spot advancing blocks (SAB) and transmission gates for the multiplexers to maintain the adiabatic property of the ReRoCs. The building blocks are the multi-input SABs (MISAB) and multi-output SABs (MOSAB), as illustrated in Figure 5. CLK1 through CLK8 inputs of the SABs are the multiple phases readily available on each local ReRoC building block of the SROA. In particular, CLK1 is shifted by 0° from a reference, whereas CLKN is shifted by (N-1)\*360/N degrees. The dynamic frequency division, with improved granularity proposed in this work is accomplished by topologically changing the connections CLK1 through CLK8 shown in Figure 5.

# C. Prior Work

The existing resonant DVFS approaches have relatively low frequency scalability and require bulky inductors and capacitors [5, 12–14] making it challenging to achieve high energy efficiency. On-chip SCVRs have been prototyped targeting high conversion efficiency [2, 3]. These prior works achieve good conversion efficiencies but require robust multiphase non-overlapping clock signals. The generation and synchronization of the input clock signal to each multi-phase voltage regulator (MPVR) stage becomes quite costly and even

Fig. 6. FOPAC device: MPVR architecture with ReRoCs.

unfeasible when the number of phases is very high [15, 16]. A prototype implementation for the MPVRs utilized ring oscillators to generate the multi-phase clock signals [15]. Prototype implementations of ReRoCs on silicon have been presented to explore the energy efficiency and the multiple phases [9, 17]. Rotary clock based distribution networks have been well studied in recent years focusing on optimization of the local and global clock networks [10, 18-22].

# **III. PROPOSED FOPAC ARCHITECTURE**

Flexible on-chip power and clock (FOPAC) architecture encompasses the FOPAC circuit building blocks, as illustrated in Figure 3, distributed through a circuit, as illustrated in Figure 1, using an ASIC-flow-compliant methodology. The onchip voltage regulators are distributed throughout the power grid and the ReRoCs are distributed locally. The FOPAC methodology is detailed in the following sections, first focusing on DVFS operation (Section III-A and Section III-B) and next on describing the integration with standard ASIC flow (Section III-C).

# A. Dynamic Voltage Scaling with MPVR

The circuit topology for the proposed MPVR, which is an integrated SCVR with ReRoC for FOPAC, is illustrated in

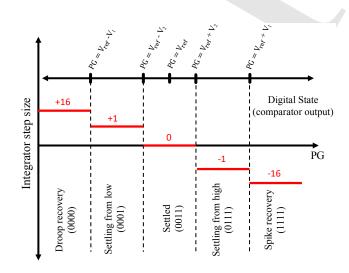

Figure 6. MPVRs are designed with ReRoCs that provide the multiple clock phases for the interleaved operation. The voltage ripple across the capacitor is reduced with multiphase interleaving [3, 8], and the ReRoCs provide higher granularity of phases. The proposed novelties in the adaptive gain comparators and the integrator logic in the feedback loop are illustrated in Figure 6 and 7, respectively. The comparators that provide high gain in the design are driven by a higher frequency clock signal  $(CLK_{Hf})$  whereas the comparators that provide nominal gain by a lower frequency clock signal ( $CLK_{Lf}$ ) [23]. This significantly improves the speed of the regulation at the output of the MPVR while also maintaining the stability of the control loop. The two different frequencies of the clock signal are provided from the same ReRoC, with the minimal overhead of an additional frequency divider. The comparator architecture is chosen as double-tail latch-type for speed and low kickback noise. To increase the settling speed of the integrator, several integrator regions that have different step sizes based on the difference in between the output and reference voltages are designed. This technique helps the integrator to keep up with the actual current requirement at the output rather than setting it to the maximum value for fast recovery [8].

Overall, one ReRoC structure with k dividers can provide the k distinct clock frequencies for comparator operation, and

Fig. 8. ReRoC with divider placement.

$100\,\mathrm{pF}$

4

100

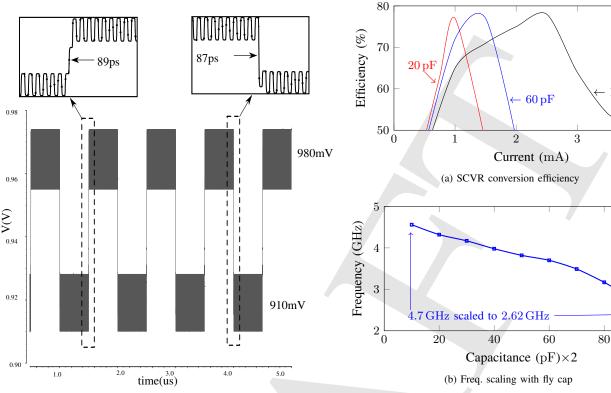

Fig. 9. MPVR symmetric step up and step down scaling, with reference voltages of  $980\,\mathrm{mV}$  and  $910\,\mathrm{mV}$ .

the *m* multi-phase signals, shown in Figure 6 for k=2 (i.e. for  $\text{CLK}_{Hf}$  and  $\text{CLK}_{Lf}$ ). ReRoCs are designed in the GHz frequency range and the clock for the SCVR is generated after frequency division and duty cycle conversion. The placement of the frequency dividers with respect to the ReRoC rings is illustrated in Figure 8. It is straight forward to tap the *m* multi-phase clock sources for the SCVRs since the tapping locations are accurately known and the routing not as complex as clock distribution networks accomplished in [21]. Consider the tapping point for a particular phase  $\Theta_{P_i}$  to be located at (x,y). The SCVR clock source taps onto  $\Theta_{P_i}$  that satisfies the phase requirement. The placement of the SCVR depends on: i)  $\Theta_{SCVR_p}$  - the phase required for the SCVR and ii)  $\Theta_{l_i}$  the phase attributed to the tapping wire  $l_i$ . The SCVR is placed such that  $\Theta_{SCVR_p} = \Theta_{l_i} + \Theta_{P_i}$ .

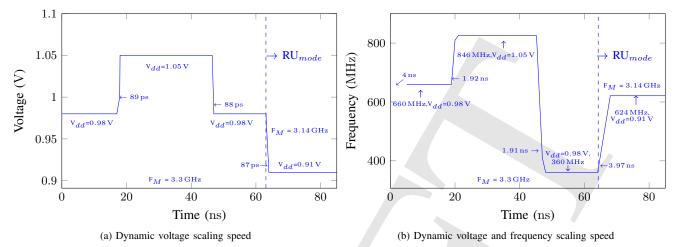

Two sets of results are presented to validate and measure the effectiveness of the DVS operation with MPVR. The first set of results is the symmetric and fast response to both stepup and step-down changes in the reference voltage of the MPVR with an output current of 50 mA (arbitrarily selected) shown in Figure 9. The high gain comparators are clocked at an arbitrarily selected ReRoC frequency of 3.3 GHz (CLK<sub>*Hf*</sub> in Figure 6). The nominal gain comparators (CLK<sub>*Lf*</sub> in Figure 6) and MPVRs are clocked at 360 MHz after performing frequency division by 9. Step-up and step-down scaling with MPVRs takes 89 ps and 87 ps, respectively. The robust ReRoC signals with accurate phase matching between the SCVRs and ReRoCs along with the digital control helps in achieving the symmetric step-up and step-down scaling of the MPVRs.

Fig. 10. Power conversion efficiency of SCVRs and frequency scaling of ReRoC with fly caps.

A maximum voltage ripple of 20 mV is achieved with 18 interleaved stages of the MPVR.

The second set of results for DVS scaling with MPVR are based on the fly capacitor selection on i) SCVR conversion efficiency and ii) the opportunistic design assisting DFS. In Figure 10(a), the voltage conversion efficiency  $\eta_{SCVR}$  for different fly capacitor values is shown. The overall power efficiency of the SCVR is computed as,

$$\eta_{SCVR} = \frac{P_{out}}{P_{out} + P_{sw} + P_{buff} + P_{control} + P_{par}}.$$

(2)

In Eq. (2),  $P_{out}$ ,  $P_{sw}$ ,  $P_{buff}$ ,  $P_{par}$ , and  $P_{control}$  are the output power, switching power, buffer power, parasitic power, and control and reference circuit related power, respectively. These values are obtained from SPICE simulations of extracted layouts of a FOPAC designed in a 65 nm technology. The (known) impact of the fly capacitor size on the maximum power efficiency is for varying load current is shown in Figure 10(a). The fly capacitors can be split to achieve maximum power efficiency for varying load currents.

In the FOPAC architecture, fly capacitors connected to the ReRoCs can optionally be used to lower the frequency. Frequency scaling with different fly capacitor values on an arbitrarily selected ReRoC frequency of 4.7 GHz is shown in Figure 10(b). The fly capacitors are split to achieve finer granularity of frequency scaling. This design parameter of fly capacitors supplements the DFS operation provided by the resonant rotary divider (Section III-B), enabling even finer control of the DFS operation in FOPAC.

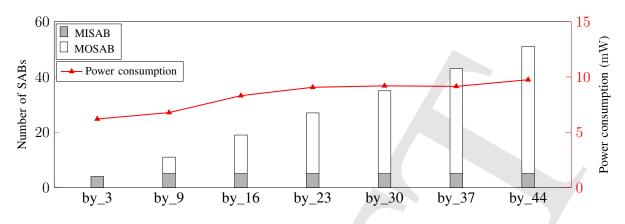

Fig. 11. Power consumption of the dynamic frequency divider, 6 main-loops and 1 sub-loop.

TABLE I DYNAMIC FREQUENCY SCALING WITH DIVIDER.

| Div   | ReRoC master clock 2.5 GHz |                  |          | ReRoC master clock 4.2 GHz |                  |          | ReRoC master clock 5 GHz |                  |          |

|-------|----------------------------|------------------|----------|----------------------------|------------------|----------|--------------------------|------------------|----------|

| ratio | Power                      | Power normalized | DFS time | Power                      | Power normalized | DFS time | Power                    | Power normalized | DFS time |

|       | (mW)                       | to div ratio 44  | (ns)     | (mW)                       | to div ratio 44  | (ns)     | (mW)                     | to div ratio 44  | (ns)     |

| 3     | 7.32                       | $0.67 \times$    | 1.18     | 5.20                       | 0.59×            | 0.72     | 4.31                     | $0.55 \times$    | 0.59     |

| 9     | 7.90                       | $0.73 \times$    | 1.19     | 5.78                       | 0.66×            | 0.69     | 4.89                     | $0.62 \times$    | 0.60     |

| 16    | 9.43                       | $0.87 \times$    | 1.19     | 7.31                       | $0.84 \times$    | 0.71     | 6.42                     | $0.82 \times$    | 0.61     |

| 23    | 10.18                      | $0.94 \times$    | 1.21     | 8.07                       | 0.92×            | 0.70     | 7.18                     | 0.91×            | 0.60     |

| 30    | 10.32                      | $0.95 \times$    | 1.20     | 8.20                       | $0.94 \times$    | 0.71     | 7.31                     | 0.93×            | 0.60     |

| 37    | 10.27                      | $0.94 \times$    | 1.19     | 8.15                       | 0.93×            | 0.72     | 7.26                     | $0.92 \times$    | 0.60     |

| 44    | 10.87                      | $1 \times$       | 1.19     | 8.74                       | 1×               | 0.68     | 7.86                     | 1×               | 0.59     |

| Avg.  | 9.47                       | 0.85 	imes       | 1.19     | 7.35                       | 0.81×            | 0.70     | 6.46                     | 0.79×            | 0.60     |

#### B. Dynamic Frequency Scaling of ReRoC

In the dynamic ReRoC frequency divider, illustrated in Figure 5, the phase delay between the adjacent MOSABs in the main-loop is expressed as  $((m-1)/m) \cdot 2\pi$  and the phase delay between the MISABs in the sub-loop is expressed as  $((m-2)/m) \cdot 2\pi$  [11]. When  $n_1$  is the number of connections between the MOSABs in the main-loop, and  $n_2$  is the number of connections between the MISABs and MOSABs in the main-loop and sub-loop, then the number of connections required to perform a division of ratio r is,

$$\left(n_1 \cdot \frac{m-1}{m}\right) \cdot 2\pi + \left(n_2 \cdot \frac{m-2}{m}\right) \cdot 2\pi = r \cdot 2\pi.$$

(3)

The m phases of the ReRoCs are used to produce the frequency divider output. When m = 8, the phase delays between the adjacent SABs in the main-loop is  $7/8 \cdot 2\pi$  and the sub-loop is  $6/8 \cdot 2\pi$ , as illustrated in Figure 5. From Eq (3), to perform a frequency division of r = 9,  $n_1 = 6$ and  $n_2 = 5$  connections are required. This can be achieved with a circuit topology similar but not identical to that in Figure 5. The proposed topology is not identical because for  $r = 10, n_1 = 8$  and  $n_2 = 4$ , connections would be required, which are higher than the available SABs in Figure 5 [11]. A modified topology is proposed in this paper in order to perform frequency division greater than 9. The main-loop in Figure 5 is stacked with an additional main-loop. An increase in the number of the main-loops requires larger multiplexers to enable the selection between the main-loops and the sub-loop. In [11], it is shown that restricting the number of MISABs in the sub-loop is desirable for power savings and lower area. Stacking additional main-loops, any integer division ratio from 3 to n can be achieved, at limited power and area cost. This is achieved by implementing the smallest number of  $n_1$  and  $n_2$  desirable for power savings and area reduction from Eq. (3).

The power consumption of the frequency dividers for division ratios 3 to 44 with a master clock of 3.3 GHz is shown in Figure 11. The total number of MISABs and MOSABs increases monotonically along with the division ratio. The power

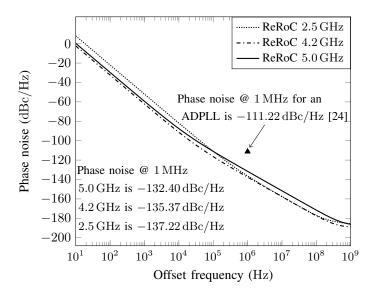

Fig. 12. Phase noise versus offset frequency of the ReRoCs.

consumption however does not increase monotonically due to the adiabatic nature of the resonant frequency dividers and the selection lines for the DFS. The switching time between frequency domains is approximately 3 clock cycles ( $\approx 0.60$  ns for a 5 GHz clock). Experiments are repeated for arbitrarily selected master clock frequencies of 2.5 GHz, 4.2 GHz, and 5 GHz, demonstrating similar trends of sub-linearly increasing power dissipation with increasing divider value and under 3 clock cycles of switching time for DFS as shown in Table I.

In Figure 12, the phase noise of the ReRoCs designed for Table I is plotted. The phase noise of the 2.5 GHz ReRoC at an offset frequency of 1 MHz is  $-137.22 \,\mathrm{dBc/Hz}$ . The phase noise for the 4.2 GHz and 5 GHz master clock frequencies are  $-135.37 \,\mathrm{dBc/Hz}$  and  $-132.40 \,\mathrm{dBc/Hz}$ , respectively. An all digital phase locked loop (ADPLL) manufactured in the 65 nm SOI technology node with an output frequency of 4 GHz has a phase noise of  $-111.22 \,\mathrm{dBc/Hz}$  at an offset frequency of 1 MHz [24].

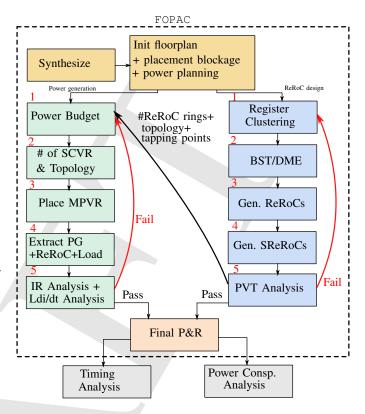

# C. FOPAC Methodology

The novelties of this work are embedded into the FOPAC methodology, compliant with the traditional ASIC flow, as illustrated in Figure 13. First, the design is synthesized with an industrial tool and undergoes initial placement, power planning, and placement blockages for the ReRoCs. Then, the designs undergo ReRoC design and power generation. The custom flows enabling FOPAC are as follows:

1) ReRoC design: The custom ReRoC clock distribution network synthesis has five steps, illustrated in Figure 13.

- 1) Register clustering to generate balanced capacitance load clusters.

- 2) BST/DME to generate an unbuffered steiner tree for each cluster [25].

- ReRoC topology generation with the dynamic frequency dividers.

- 4) Generation of synchronous distribution aware sparse ReRoCs (SReRoC) [10].

- 5) Physical connections translation to a netlist and PVT analysis of the clock distribution network.

Step 1 and step 2 constitute the subnetwork tree generation process for a bottom-up clock tree synthesis (CTS) process. The clock network and distribution are designed to be correct by design, thanks to steps 1 through 4, concluding with the PVT analysis with SPICE-accurate verification in step 5. The proposed steps for ReRoC are similar to [26], where [26] details the automation of resonant rotary clock design for any ASIC design. ReRoC is differentiated from [26] in codesigning clock and power, i.e. the power planning input to the ReRoC Stage has pervasive impact on the ReRoC design, as the fly capacitors are opportunistically shared.

2) *Power generation:* The power generation (and distribution) has five steps, illustrated in Figure 13.

- 1) Power budget estimation for the design.

- 2) Determination of the number of SCVRs and topology.

- 3) Placement of the MPVR.

- Power grid extraction along with the ReRoCs and core load.

Fig. 13. FOPAC Methodology.

#### 5) Worst case static IR and Ldi/dt analysis.

The input to Step 1 is the topology of the ReRoC rings including the number of ReRoC rings and tapping points for the multiple phases required for the MPVRs from the ReRoC design flow. For a given power budget, an SCVR topology is designed with the goal of achieving the desired target efficiency by distributing the power budget over multiple SCVRs. The number of SCVRs required is divided such that each ReRoC ring has a voltage regulator (with load balancing) and the rest of the design has the appropriate number of voltage regulators necessary to operate during the low performance mode. Similar to use of PVT analysis in ReRoC design for DFS, the power generation stage utilizes SPICE simulations in step 5 for signal integrity analysis of DVS operation.

# IV. FOPAC EVALUATION

FOPAC is demonstrated on three different industrial designs that are publicly available: 1) *AES* encryption core, 2) *Arm core* - CORTEX M0, and 3) *VSCALE* RISC-V. The designs are placed and routed (P&R) and subjected to STA in order to verify the timing of the ASIC flow at the system level. The timing and power characteristics of the FOPAC components (ReRoC and MPVR) are analyzed in deeper detail through SPICE simulations of layout-extracted models that include parasitics. In particular, the transmission line interconnect parasitics are extracted using the high frequency structural simulator (HFSS). The algorithms are implemented

Fig. 14. FOPAC DVFS operation on the RISC-V core.

in C++ and Matlab. An industrial 65 nm technology library is used for the evaluation.

The simulations results and conclusions are presented within three major categories:

- 1) FOPAC DVFS operation,

- FOPAC power consumption with respect to traditional systems, and

- FOPACs power consumption with respect to previous literature on resonant systems.

# A. FOPAC DVFS Operation

An arbitrary ReRoC frequency of 3.3 GHz ( $F_M$ ) is chosen to evaluate the FOPAC methodology. Two sets of dynamic resonant frequency dividers to perform frequency division in integer ratios 3 to 9 are designed for the core clock source ( $F_{core}$ ) and the MPVR clock source ( $F_{mpvr}$ ). In the PVT stage, the geometries of the ReRoC rings along with the frequency dividers are varied ±10% to represent the worst case scenarios. The deviation from the target frequency of 3.3 GHz with PVT variations for 500 Monte-Carlo runs are presented in Table II. Average frequency variations of <1% and <0.6% are observed under intra- and inter-die variations, respectively. Worst case static IR and Ldi/dt analysis are performed on the layout extracted industrial designs (RLC models). The average worst case voltage drop across the three industrial designs is 2.1% of the  $V_{dd}$ .

A sample operation of FOPAC DVFS operation of the RISC-V core is presented in Figure 14, prior to the presentation of the performance comparisons to prior work in literature

TABLE II PVT, IR and Ldi/dt Analysis results.

| Design        | PVT (500 Mor     | Static IR        |          |

|---------------|------------------|------------------|----------|

|               | Max. intra-die   | Max. inter-die   | & Ldi/dt |

| AES cipher    | 31 MHz           | 15 MHz           | 2.1%     |

| CORTEX M0     | $35\mathrm{MHz}$ | 17 MHz           | 1.9%     |

| VSCALE RISC-V | $28\mathrm{MHz}$ | $24\mathrm{MHz}$ | 2.4%     |

| Average       | $30\mathrm{MHz}$ | 19 MHz           | 2.1%     |

in Tables III and IV. The switching speed between different frequency domains is <1 ns ( $\approx 3$  cycles of  $F_M$ ). At the start, it takes 3 ns for the ReRoC oscillations to sustain at  $3.3 \,\mathrm{GHz}$  (F<sub>M</sub>). After which a divide by 5 is performed to generate the 660 MHz clock for the core ( $F_{core}$ ) and divide by 9 to generate the 360 MHz clock ( $F_{mpvr}$ ) for the MPVRs at  $V_{dd}$  = 0.98 V (nominal). The high gain comparators are clocked at  $F_M$  and nominal gain comparators are clocked at  $F_{mpvr}$ . The frequency  $F_{core}$  and voltage are scaled between different levels to validate the accuracy of the switching speed. To enable the fly capacitor reuse mode  $(RU_{mode})$ , 10 of the SCVRs are shut down and the fly capacitor is loaded to the ReRoC rings in the RISC-V core. In the RUmode, it takes  $\approx 3 \,\mathrm{ns}$  for the frequency of the ReRoC F<sub>M</sub> to stabilize to 3.14 GHz (with voltage scaling). Then, it takes 0.97 ns to scale  $F_{core}$  to 624 MHz and  $F_{mpvr}$  to 348 MHz to operate the RISC-V core in the  $RU_{mode}$  with  $V_{dd} = 0.91$  V. In total, it takes  $3.97 \,\mathrm{ns}$  to scale the frequency to the RU<sub>mode</sub> at run time by utilizing the fly capacitor of the SCVRs.

#### B. FOPAC power consumption

The power consumption of the FOPAC based designs versus PLL based designs operating at 825 MHz is presented in Table III. The PLL-based design is built with a traditional PLL from a cell library used on the ASIC implementations performed with Cadence Innovus. Power measurements are presented for the PLL only, labeled PLL<sub>clock</sub> in Table III, and for the entire design, labeled PLL<sub>core</sub> in Table III. The power of the SCVRs, the frequency dividers, and the control circuit is included in FOPACcore. The PLL based designs and FOPAC based designs have the same number of SCVRs. The clock source for the SCVRs in the PLL based designs are ring oscillators [15]. A total power saving of 36% is achieved for the circuits (FOPAC<sub>core</sub>) when compared against a PLL clocked core (PLL<sub>core</sub>). The clock power savings are significant for the clocks: 67% power savings (FOPAC<sub>clock</sub>) when compared against a PLL based design ( $PLL_{clock}$ ).

TABLE IIIPOWER CONSUMPTION OF PLL DESIGN VERSUS FOPAC OPERATING AT FREQ= 825 MHz,  $V_{dd}$ = 0.98 V, and Temp.=  $25 \degree$ C.

| Design        | Num.  | PLL clocked design   |                     | FOPAC                  |                 |       |  |

|---------------|-------|----------------------|---------------------|------------------------|-----------------|-------|--|

|               | SCVRs | PLL <sub>clock</sub> | PLL <sub>core</sub> | FOPAC <sub>clock</sub> | FOPACcore       | Num.  |  |

|               |       | power (mW)           | power (mW)          | power (mW)             | power (mW)      | ReRoC |  |

| AES cipher    | 8     | 18.17                | 57.60               | 5.96 (-67.19%)         | 37.87 (-34.25%) | 4     |  |

| CORTEX M0     | 12    | 26.04                | 73.74               | 9.34 (-64.13%)         | 45.56 (-38.21%) | 6     |  |

| VSCALE RISC-V | 16    | 41.21                | 108.28              | 12.78 (-68.98%)        | 69.04 (-36.23%) | 10    |  |

| Average       | -     | -                    | -                   | -67%                   | -36%            | -     |  |

TABLE IV

COMPARISON OF FOPAC WITH PRIOR WORKS.

| Design                      | Restle [5]                      | Rahman [12]                  | Lu [15]                        | This work FOPAC                 |

|-----------------------------|---------------------------------|------------------------------|--------------------------------|---------------------------------|

|                             | ISSCC 2014                      | JSSC 2018                    | ISSCC 2015                     | (SPICE)                         |

| Technology                  | 22 nm SOI                       | 65 nm bulk                   | 65 nm bulk                     | 65 nm <b>bulk</b>               |

| Clock source                | PLL+resonant grid               | PLL+resonant grid            | VCO                            | ReRoC                           |

| System resonant             | Always                          | Always                       | No                             | Always                          |

| Resonant DVFS               | No                              | Yes                          | No, DVS only                   | Yes                             |

| Voltage range               | $0.75 \text{-} 1.05 \mathrm{V}$ | $0.7 	ext{-} 1.2 \mathrm{V}$ | 0.6-1.2 V                      | <b>0.9-</b> 1.2 V               |

| Frequency range             | $2.5-5\mathrm{GHz}$             | DC-132 MHz                   | -                              | 348 MHz-1.1 GHz*                |

| Inductor                    | On chip                         | Off chip                     | -                              | No                              |

|                             | (0.3-2.5 nH each)               | (7 nH)                       |                                |                                 |

| Voltage regulator (VR)      | Yes                             | No                           | Yes                            | Yes                             |

| DVS speed                   | DNR                             | -                            | $2.5 \mathrm{V}/\mu\mathrm{s}$ | $7.86\mathrm{V}/\mathrm{\mu s}$ |

| $\eta_{max}$ of VR          | DNR                             | -                            | 78.3%                          | 77%                             |

| $\rho (W/mm^2) @\eta_{max}$ | DNR                             | -                            | 0.152                          | 0.017                           |

| Power reduction             | 36%                             | 34%-38%                      | -                              | 25%-39%                         |

| Clock power reduction       | -                               | -                            | -                              | 62%-74%                         |

DNR - Did not report, \* Resonant frequency divider topology dependent

#### C. FOPAC power comparison with previous works

FOPAC is compared to prior resonant works in Table IV. The numbers reported in Table IV are from SPICE simulations of the sweep of the V/f range— 0.9 to 1.2 V and 348 MHz to 1.1 GHz— over SS, FF, FS, and SF corners, and not only the results reported in Table III. Overall, FOPAC delivers power with 77% efficiency, and achieves 25%-39% power reduction thanks to 64%-74% reduction in clock power. The voltage scaling within FOPAC is symmetric and robust with a (worst-case)  $t_{response}$  of 89 ps. The DFS switching time within FOPAC utilizing a 3.3 GHz ReRoC is 0.9 ns. Overall, FOPAC demonstrates scaling of the voltage-frequency over a wide range without the need for on/off-chip inductors while re-utilizing (RU<sub>mode</sub>) the fly capacitor for higher frequency tuning.

# V. CONCLUSIONS

In this paper, the fusion of resonant rotary clock with on chip voltage regulators enabling flexible on-chip power and clock is presented. FOPAC is designed and evaluated on three different industrial designs to validate the architecture. FOPAC can switch between different V/f domains in 1.9 ns with a ReRoC clock operating at 3.3 GHz. FOPAC achieves 25% -39% power savings while offering fly capacitance re-usability to tune the ReRoC frequency at run time without any negative implications. FOPAC can provide high number of V/f domains with fast DVFS capability while consuming low-power and operating reliably, justified via evaluation on industrial designs in this work.

#### REFERENCES

- K. Shu, E. Sanchez-Sinencio, J. Silva-Martinez, and S. H. K. Embabi, "A 2.4-ghz monolithic fractional-n frequency synthesizer with robust phaseswitching prescaler and loop capacitance multiplier," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 38, no. 6, pp. 866–874, June 2003.

- [2] H. P. Le, S. R. Sanders, and E. Alon, "Design techniques for fully integrated switched-capacitor dc-dc converters," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 46, no. 9, pp. 2120–2131, Sept 2011.

- [3] Y. K. Ramadass, A. A. Fayed, and A. P. Chandrakasan, "A fullyintegrated switched-capacitor step-down dc-dc converter with digital capacitance modulation in 45 nm cmos," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 45, no. 12, pp. 2557–2565, Dec 2010.

- [4] S. R. Sanders, E. Alon, H. Le, M. D. Seeman, M. John, and V. W. Ng, "The road to fully integrated dc-dc conversion via the switched-capacitor approach," *IEEE Transactions on Power Electronics (TPE)*, vol. 28, no. 9, pp. 4146–4155, Sept 2013.

- [5] P. Restle, D. Shan, D. Hogenmiller, Y. Kim, A. Drake, J. Hibbeler, T. Bucelot, G. Still, K. Jenkins, and J. Friedrich, "5.3 wide-frequencyrange resonant clock with on-the-fly mode changing for the POWER8 microprocessor," in *Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC)*, Feb 2014, pp. 100–101.

- [6] G. Villar-Pique, H. J. Bergveld, and E. Alarcon, "Survey and benchmark of fully integrated switching power converters: Switched-capacitor versus inductive approach," *IEEE Transactions on Power Electronics (TPE)*, vol. 28, no. 9, pp. 4156–4167, September 2013.

- [7] O. A. Uzun and S. Kose, "Converter-gating: A power efficient and secure on-chip power delivery system," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS)*, vol. 4, no. 2, pp. 169–179, June 2014.

- [8] H. P. Le, J. Crossley, S. R. Sanders, and E. Alon, "A sub-ns response fully integrated battery-connected switched-capacitor voltage regulator delivering 0.19W/mm<sup>2</sup> at 73% efficiency," in *International Solid-State Circuits Conference (ISSCC)*, Feb 2013, pp. 372–373.

- [9] J. Wood, T. C. Edwards, and S. Lipa, "Rotary traveling-wave oscillator arrays: a new clock technology," *IEEE Journal of Solid-State Circuits* (JSSC), vol. 36, no. 11, pp. 1654–1665, Nov 2001.

- [10] Y. Teng and B. Taskin, "Sparse-rotary oscillator array (sroa) design for power and skew reduction," in *Proceedings of the Design, Automation* and Test in Europe Conference Exhibition (DATE), March 2013, pp. 1229–1234.

- [11] —, "Resonant frequency divider design methodology for dynamic frequency scaling," in *Proceedings of the International Conference on Computer Design (ICCD)*, Oct 2013, pp. 479–482.

- [12] F. U. Rahman and V. Sathe, "Quasi-resonant clocking: Continuous voltage-frequency scalable resonant clocking system for dynamic voltage-frequency scaling systems," *IEEE Journal of Solid-State Circuits* (JSSC), vol. 53, no. 3, pp. 924–935, March 2018.

- [13] L. G. Salem and P. P. Mercier, "A 0.4-to-1V 1MHz-to-2GHz switchedcapacitor adiabatic clock driver achieving 55.6% clock power reduction," in *Proceedings of the International Solid-State Circuits Conference (ISSCC)*, Feb 2017, pp. 442–443.

- [14] H. Fuketa, M. Nomura, M. Takamiya, and T. Sakurai, "Intermittent resonant clocking enabling power reduction at any clock frequency for near/sub-threshold logic circuits," *IEEE Journal of Solid-State Circuits* (JSSC), vol. 49, no. 2, pp. 536–544, Feb 2014.

- [15] Y. Lu, J. Jiang, W.-H. Ki, C. P. Yue, S.-W. Sin, S.-P. U, and R. P. Martins, "A 123-phase DC-DC converter-ring with fast-DVS for microprocessors," in *Proceedings of the International Solid-State Circuits Conference (ISSCC)*, Feb 2015, pp. 1–3.

- [16] Y. Lu, J. Jiang, and W. Ki, "Design considerations of distributed and centralized switched-capacitor converters for power supply on-chip," *IEEE Journal of Emerging and Selected Topics in Power Electronics (JESTPE)*, vol. 6, no. 2, pp. 515–525, June 2018.

- [17] A. Martchovsky and K. D. Pedrotti, "Amplifier innovations for improvement of rotary traveling wave oscillators," *IEEE Transactions on Circuits* and Systems I: Regular Papers (TCAS-I), vol. PP, no. 99, pp. 1–9, 2017.

- [18] G. Venkataraman, J. Hu, F. Liu, and C. N. Sze, "Integrated placement and skew optimization for rotary clocking," in *Proceedings of the Design Automation and Test in Europe Conference (DATE)*, vol. 1, March 2006, pp. 1–6.

- [19] Z. Yu and X. Liu, "Design of rotary clock based circuits," in *Proceedings* of the Design Automation Conference (DAC), June 2007, pp. 43–48.

- [20] J. Lu, V. Honkote, X. Chen, and B. Taskin, "Steiner tree based rotary clock routing with bounded skew and capacitive load balancing," in *Proceedings of the Design, Automation and Test in Europe (DATE)*, March 2011, pp. 1–6.

- [21] V. Honkote and B. Taskin, "Croa: Design and analysis of the custom rotary oscillatory array," *IEEE Transactions on Very Large Scale Inte*gration Systems (TVLSI), vol. 19, no. 10, pp. 1837–1847, Oct 2011.

- [22] X. Hu and M. R. Guthaus, "Distributed LC resonant clock grid synthesis," *IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)*, vol. 59, no. 11, pp. 2749–2760, Nov 2012.

- [23] O. A. Uzun, "Speed, power efficiency, and noise improvements for switched capacitor voltage converters," *Thesis, University of South Florida*, 2017.

- [24] J. A. Tierno, A. V. Rylyakov, and D. J. Friedman, "A wide power supply range, wide tuning range, all static cmos all digital pll in 65 nm soi," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 43, no. 1, pp. 42–51, Jan 2008.

- [25] K. D. Boese and A. B. Kahng, "Zero-skew clock routing trees with minimum wirelength," in *Proceedings of the IEEE International ASIC Conference and Exhibit (ASIC)*, Sep 1992, pp. 17–21.

- [26] R. Kuttappa, A. Balaji, V. Pano, B. Taskin, and H. Mahmoodi, "RotaSYN: Rotary Traveling Wave Oscillator SYNthesizer," *IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)*, January 2019.

Ragh Kuttappa (S'15) received the Bachelor's degree from Visvesvaraya Technological University, India, in 2012 and the Master's degree from San Francisco State University, San Francisco, CA, in 2015. He is currently pursuing the Ph.D. degree from the Department of Electrical and Computer Engineering, Drexel University, Philadelphia, PA. His current research interests include electronic design automation for VLSI, low-power circuits and resonant clocking. He has held an intern position at Samsung Austin Research Center (SARC) in 2017.

Selçuk Köse (S'10-M'12) received the B.S. degree in electrical and electronics engineering from Bilkent University, Ankara, Turkey, in 2006 and the M.S. and Ph.D. degrees in electrical engineering from the University of Rochester, Rochester, NY, USA, in 2008 and 2012, respectively.

He was with TUBITAK, Ankara, Intel Corporation, Santa Clara, CA, USA, and Freescale Semiconductor, Tempe, AZ, USA. He is currently an Associate Professor at the Department of Electrical Engineering, University of Rochester, Rochester,

NY, USA. Prior to joining University of Rochester, he was an Assistant Professor at the University of South Florida, Tampa, FL, USA. His current research interests include integrated voltage regulation, 3-D integration, hardware security, and green computing.

Dr. Kose was a recipient of the NSF CAREER Award, the Cisco Research Award, the USF College of Engineering Outstanding Junior Researcher Award, and the USF Outstanding Faculty Award. He is an Associate Editor of the Journal of Circuits, Systems, and Computers and Microelectronics Journal. He has served on the Technical Program and Organization Committees of various conferences.

**Baris Taskin** (S'01-M'05-SM'12) received the B.S. degree in electrical and electronics engineering from Middle East Technical University, Ankara, Turkey, in 2000, and the M.S. and Ph.D. degrees in electrical engineering from the University of Pittsburgh,Pittsburgh, PA, in 2003 and 2005, respectively.

Dr. Taskin is currently a Professor of Electrical and Computer Engineering at Drexel University, Philadelphia, PA. His current research interests include electronic design automation for VLSI, low-

power circuits, resonant clocking, clock network synthesis, wireless IC interconnects, and networks-on-chip for chip multiprocessors.

Dr. Taskin is a recipient of a number of awards for his research and professional contributions, including the National Science Foundation Faculty Early Career Development (NSF CAREER) Award in 2009, an ACM SIGDA Distinguished Service Award in 2012 and the Delaware Valley Young Electrical Engineer of the Year Award from the IEEE Philadelphia Section in 2013 and the Drexel ECE Department's Outstanding Research Award in 2015. Dr. Taskin is the General Chair for ACM Great Lakes Symposium on VLSI (GLSVLSI) 2019 and is the Chair of the IEEE Circuits and Systems Society's Technical Committee on VLSI Systems and Applications (IEEE CAS VSA-TC) 2018-2020.