Ragh Kuttappa: Difference between revisions

| Line 59: | Line 59: | ||

====Journals==== | ====Journals==== | ||

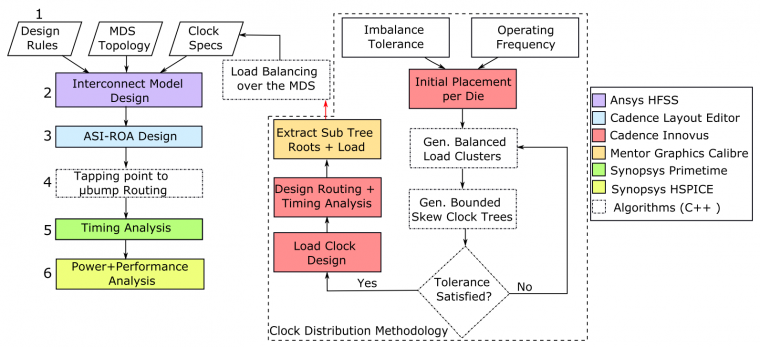

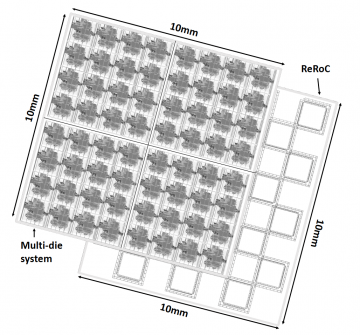

# Ragh Kuttappa, Baris Taskin, Scott Lerner, and Vasil Pano, "Resonant Clock Synchronization with Active Silicon Interposer for Multi-Die Systems", ''IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)'', | # Ragh Kuttappa, Baris Taskin, Scott Lerner, and Vasil Pano, "Resonant Clock Synchronization with Active Silicon Interposer for Multi-Die Systems", ''IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)'', Vol. 68, No. 4, pp. 1636-1645, April 2021. | ||

# Ragh Kuttappa, Selcuk Kose, and Baris Taskin, "FOPAC: Flexible On-Chip Power and Clock", ''IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)'', Vol. 66, No. 12, pp. 4628--4636, December 2019. | # Ragh Kuttappa, Selcuk Kose, and Baris Taskin, "FOPAC: Flexible On-Chip Power and Clock", ''IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)'', Vol. 66, No. 12, pp. 4628--4636, December 2019. | ||

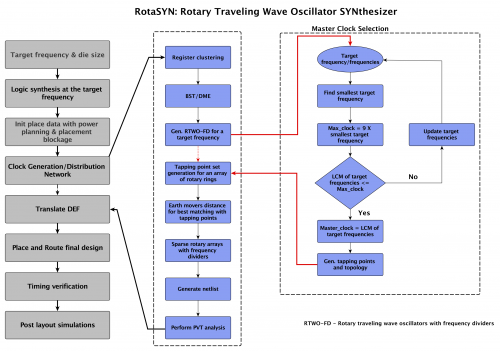

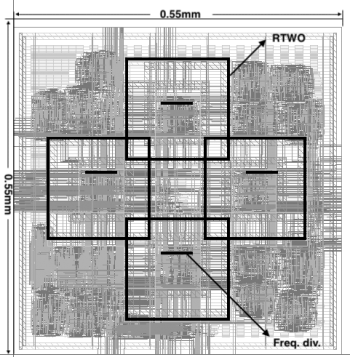

# Ragh Kuttappa, Adarsha Balaji, Vasil Pano, Baris Taskin, and Hamid Mahmoodi, "RotaSYN: Rotary Traveling Wave Oscillator SYNthesizer", ''IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)'', Vol. 66, No. 7, pp. 2685--2698, July 2019. | # Ragh Kuttappa, Adarsha Balaji, Vasil Pano, Baris Taskin, and Hamid Mahmoodi, "RotaSYN: Rotary Traveling Wave Oscillator SYNthesizer", ''IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I)'', Vol. 66, No. 7, pp. 2685--2698, July 2019. | ||

Revision as of 12:10, 6 March 2021

Education

Ph.D. in Electrical Engineering, ongoing

- Drexel University, Philadelphia, PA, USA

M.S. in Electrical Engineering, 2015

- San Francisco State University

Bachelor of Engineering, 2012

- Visvesvaraya Technological University (VTU), Karnataka, India

Research Interests

- Resonant clocking technologies

- Adiabatic circuits

- Nanoscale circuits and systems

- Low-power design methodologies

Resonant clocking technologies

Resonant clocking is a low power clock generation and distribution solution for modern ICs. The main research focus is the design and implementation of rotary clocks that is interoperable within the traditional ASIC flow. Based on years of development and experience within Dr. Taskin's research group numerous products for rotary clocks are currently being developed to address future needs for energy efficient computing.

1. RotaSYN: Rotary Traveling Wave Oscillator SYNthesizer

RotaSYN is a backend synthesis tool for rotary clocks. RotaSYN is demonstrated on publicly available designs and compared to traditionally clocked designs. Check out our RotaSYN PAPER published in TCAS-I.

2. Clock Synchronization for Multi-Die Systems

Multi-Die Systems (MDS) have leveraged the high interconnect performance on active and passive interposers to design Network-on-Chips (NoC). However, synchronizing the MDS with a single clocking domain has never been explored. We design a single clocking domain over the active interposer leveraging the high quality interconnect performance, specifically targeting cross-die synchronization. The underlying theme for the work is to synchronize chiplets that are in the “same clock domain”, regardless of homogeneous v.s. heterogeneous integration. Initial work and results of this work was presented at ISLPED'19. An extension of the ISLPED'19 work with a complete methodology is published in TCAS-I.

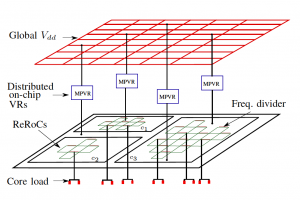

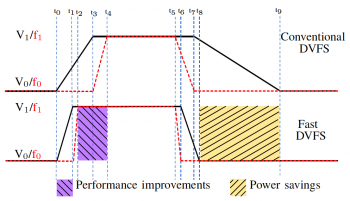

3. FOPAC: Flexible On-Chip Power and Clock

In this work we propose a novel flexible on-chip power and clock (FOPAC) generation and distribution circuit to enable fast dynamic voltage and frequency scaling (DVFS). To fuse the power and clock design, the multiphase properties of resonant rotary clocks are utilized to design multiphase voltage regulators. We also propose a capacitance reuse technique with the fly cap of switched capacitor voltage regulators to modify the frequency of the global resonant rotary clock at runtime. Check out our FOPAC PAPER published in TCAS-I.

Résumé

Publications

Journals

- Ragh Kuttappa, Baris Taskin, Scott Lerner, and Vasil Pano, "Resonant Clock Synchronization with Active Silicon Interposer for Multi-Die Systems", IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), Vol. 68, No. 4, pp. 1636-1645, April 2021.

- Ragh Kuttappa, Selcuk Kose, and Baris Taskin, "FOPAC: Flexible On-Chip Power and Clock", IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), Vol. 66, No. 12, pp. 4628--4636, December 2019.

- Ragh Kuttappa, Adarsha Balaji, Vasil Pano, Baris Taskin, and Hamid Mahmoodi, "RotaSYN: Rotary Traveling Wave Oscillator SYNthesizer", IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), Vol. 66, No. 7, pp. 2685--2698, July 2019.

- Ragh Kuttappa, Houman Homayoun, Hassan Salmani and Hamid Mahmoodi, "Reliability Analysis of Spin Transfer Torque based Look up Tables under Process Variations and NBTI Aging", Elsevier Microelectronics Reliability Journal, Vol. 62, pp. 156--166, July 2016.

Conferences

- Ragh Kuttappa, Steven Khoa, Leo Filippini, Vasil Pano, and Baris Taskin, "Comprehensive Low Power Adiabatic Circuit Design with Resonant Power Clocking", Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), May 2020.

- Ragh Kuttappa and Baris Taskin, "FinFET -- Based Low Swing Rotary Traveling Wave Oscillators", Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), May 2020.

- Karthik Sangaiah, Michael Lui, Ragh Kuttappa, Mark Hempstead, and Baris Taskin, "SnackNoc: Processing in the Communication Layer", Proceedings of the IEEE International Symposium on High-Performance Computer Architecture (HPCA) , February 2020.

- Vasil Pano, Ragh Kuttappa, and Baris Taskin, "3D NoCs with Active Interposer for Multi-Die Systems", Proceedings of the IEEE/ACM International Symposium on Networks-on-Chip (NOCS), October 2019.

- Ragh Kuttappa, Baris Taskin, Scott Lerner, Vasil Pano, and Ioannis Savidis, "Robust Low Power Clock Synchronization for Multi-Die Systems", Proceedings of the ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), July 2019.

- Longfei Wang, Ragh Kuttappa, Baris Taskin, and Selcuk Kose, "Distributed Digital Low-Dropout Regulators with Phase Interleaving for On-Chip Voltage Noise Mitigation", Proceedings of the IEEE International Workshop on System Level Interconnect Prediction (SLIP), June 2019.

- Ragh Kuttappa, Scott Lerner, Leo Filippini, and Baris Taskin, "Low Swing -- Low Frequency Rotary Traveling Wave Oscillators", Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), May 2019.

- Ragh Kuttappa and Baris Taskin, "Low Frequency Rotary Traveling Wave Oscillators", Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), May 2018.

- Ragh Kuttappa, Leo Filippini, Scott Lerner and Baris Taskin, "Stability of Rotary Traveling Wave Oscillators Under Process Variations and NBTI", Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), May 2017, pp. 1--4.

- Ragh Kuttappa, Lunal Khuon, Bahram Nabet and Baris Taskin, "Reconfigurable Threshold Logic Gates using Optoelectronic Capacitors", Proceedings of the Design, Automation and Test in Europe (DATE), March 2017, pp. 614--617.

- Ragh Kuttappa, Houman Homayoun, Hassan Salmani and Hamid Mahmoodi, "Comparative Analysis of Robustness of Spin Transfer Torque based Look Up Tables under Process Variations", Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), May 2016, pp. 606--609.

Contact Information

Address:

3141 Chestnut Street

Drexel University

ECE Department

Philadelphia, PA 19104

Office: Bossone 405

Email: fr67 [at the rate] drexel [period] edu

Linkedin: ragh/linkedin