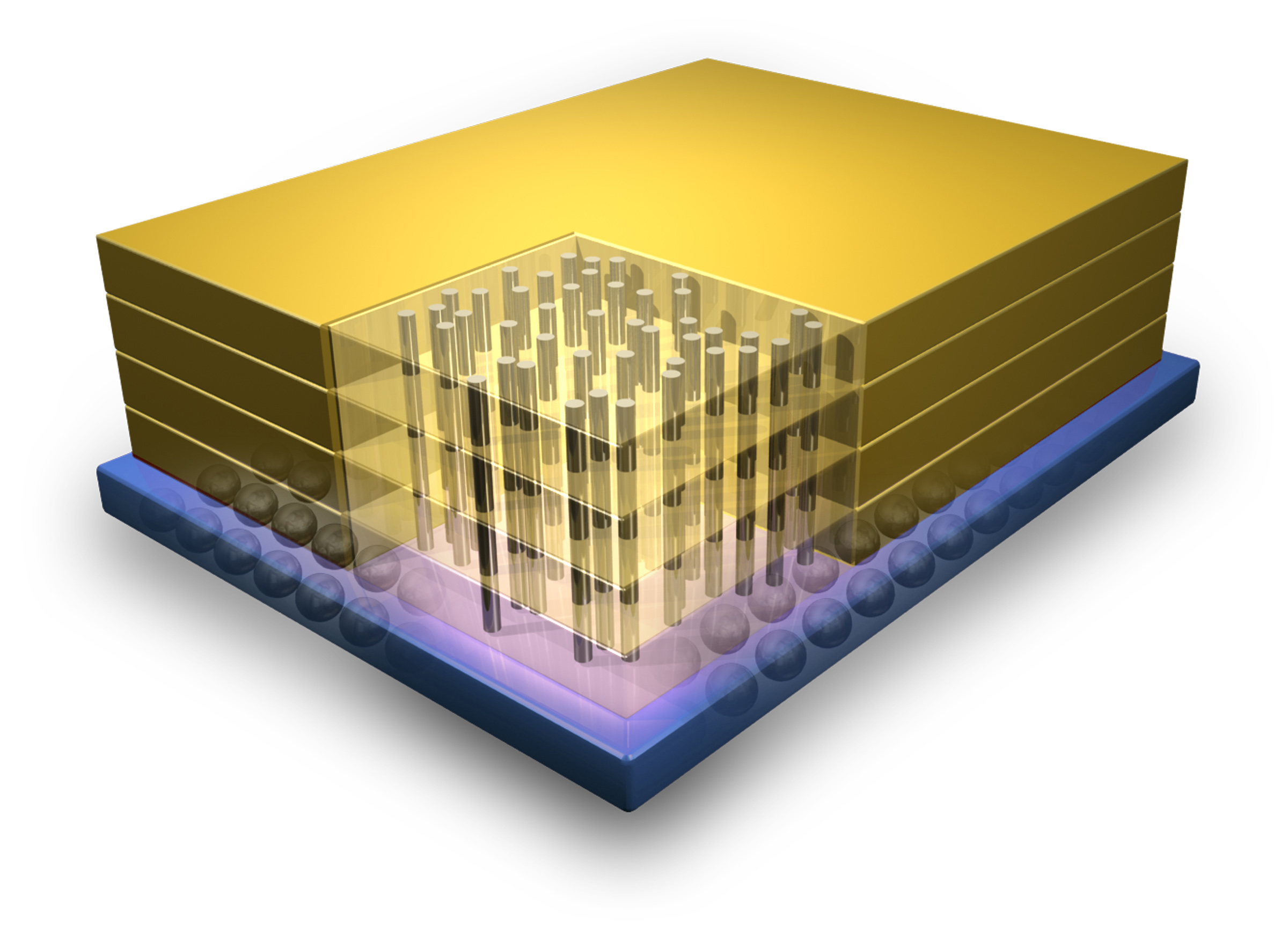

There are many design aspects that require consideration and analysis in the development of a three-dimensional integrated circuit. More specifically, when considering power delivery, synchronization, and signalling in a TSV-based 3-D IC, the potential to integrate disparate technologies with independent voltage and peak power requirements, clock speeds, thermal design power, noise requirements, and a slew of other design considerations requires new methodologies and techniques beyond which are used for two-dimensional system-on-chip integrated circuits. In addition, considerations unique to 3-D ICs such as increased hot spot formation, place and route in the z direction as well as the x and y direction, and more importantly the potential to integrate ICs from different foundaries where not all design information is shared between vendors requires not only novel methodologies and techniques, but also novel circuits at the interface between the heterogeneous device planes. In my research, I developed circuit design techniques, methodologies, and algorithms at multiple levels of abstraction as well as experimental test vehicles to provide early ground work on synchronization, power delivery, and signalling in 3-D SoC based circuits.

TSV Modeling and Characterization

The critical component of a 3-D IC is the through-silicon via. Our seminal work on the electrical characterization of the TSV resistance, capacitance, and inductance as a function of the diameter, length, dielectric thickness, and material properties of the silicon, dielectric, and metal fill initiated a slew of work on further characterizing the TSV for high frequency, different TSV placement topologies, and different physical phenomena such as depletion region formation around the TSV and interface charge trapping, which impact the TSV capacitance. Once the TSV was characterized via full wave simulation, closed-form expressions for the TSV resistance, capacitance, and inductance were developed. The closed-form expressions were compared to the simulated results, producing errors of less than 8% for the resistance, capacitance, and inductance across all diameters, lengths, dielectric thicknesses, and for frequencies upto ten GHz. An equivalent pi-model of the TSV was developed based on the closed-form expressions for TSVs produced by MIT Lincoln Laboratory and Tezzaron Semiconductor. The pi-model representation of the TSV was used for both modelling and spice analysis of the 3-D clock and power delivery networks further discussed below.

Synchronization in 3-D Integrated Circuits

Synchronization amongst various sequential elements of a two-dimensional IC is a challenge which is further exacerbated when considering a three-dimensional IC. Our work focused on multi-plane synchronization, providing an understanding of the impact that clock distribution topology has on clock skew, clock delay, signal slew, and power dissipation. A comparison of three 3-D clock distribution network topologies was performed both experimentally and through simulation. Simulations of the three clock distribution topologies also included the electrical characteristics of the TSV based on the closed-form expressions developed. The resulting modelled root to leaf delays were compared to experimental data, and good agreement was shown between the modelled and experimental results. The 3-D test circuit was designed by us and fabricated MIT Lincoln Laboratory and was composed of three device planes, 150 nm technology, and TSVs with 1.75 μm diameter and ˜10 μm length. Successful operation of the 3-D test circuit at 1.4 GHz was demonstrated. The measurements of the clock skew, clock delay, signal slew, and power dissipation suggested that each topology provides certain advantages and disadvantages in terms of different performance criteria. The proper choice, consequently, of a clock distribution network is not dictated by a single design objective but rather by the overall 3-D system design requirements including availability of resources and number of bonded planes.

Clock Tree Synthesis (CTS) for 3-D Integrated Circuits (Current)

Recent work has explored CTS for 3-D ICs by extending algorithms devised for 2D ICs such as the Methods of Means and Medians (MMM), Nearest Neighbor Graph (NNG) and Deferred Merging Algorithm (DME) for 3-D ICs. However, CTS for heterogeneous 3-D ICs has not been explored. We are developing algorithms to complete CTS for heterogeneous 3-D ICs to optimize power and minimize the skew, slew, and TSV count. In addition, TSV based 3-D IC have a large power density due to the proximity of dies. Since the power density of a 3-D IC impacts the overall system performance, the relative order of die placement in the 3-D stack can be used to manage thermals and potentially reduce the power density of the whole stack. Since the CDN consumes the majority of the power in an IC, the CTS step is ideal to find the optimum die ordering in the 3-D stack. We propose an algorithm for die ordering to minimize the power density of the overall stack. The optimal die location is then determined to place the clock source of the overall stack.

3-D Integrated Circuit Power Delivery

An important issue for 3-D integrated circuits is the design of a robust power distribution network that can provide sufficient current to every load within a system. Power delivery in 3-D integrated systems presents difficult new challenges for delivering sufficient current to each device plane. Stacking device planes in the vertical direction leads to higher power densities. Specialized techniques are required to ensure that each device plane is operational, while not exceeding the target output impedance. The focus of our research is on a primary issue in 3-D power delivery, the power distribution network, and provides a quantitative experimental analysis of the noise measured on each plane within a three plane 3-D integrated stack. A three-dimensional (3-D) test circuit examining power grid noise in a 3-D integrated stack has been designed, fabricated, and tested. Fabrication and vertical bonding were performed by MIT Lincoln Laboratory for a 150 nm, three metal layer SOI process. Three wafers were vertically bonded to form a 3-D stack. Three topologies to distribute power within a 3-D circuit have been evaluated, and an analysis of the peak noise voltage, voltage range, average noise voltage, and resonant frequency characteristics for both power and ground was performed. The effect of the through silicon via (TSV) density on the noise profile of a 3-D power delivery network is experimentally described. A comparison of the peak noise for each topology with and without board level decoupling capacitors, and resonant behavior are provided, and suggestions for enhancing the design of a 3-D power delivery network were offered. Models of the three power distribution topologies were developed and peak noise voltage and resonant frequency characteristics were compared with experimental results. This test circuit provided enhanced understanding of topology dependent noise generation and propagation in 3-D power delivery systems.

On-Chip Power Delivery with Run-Time Voltage Regulator Clustering for 3-D and 2-D ICs (Current)

With the paradigm shift in computing systems from performance oriented design to energy efficiency, there is considerable research effort to optimize the core configuration by reducing the over-provisioning of core resources which was introduced in the early part of the last decade to boost performance. However, not much attention has been given to reduce the over-provisioning of the circuits delivering power to the cores. We are developing a power delivery system for homogeneous (and heterogeneous) chip multi processor (CMP) systems which are modified at run time by clustering multiple on-chip voltage regulators (OCVR) depending on the power demand of the workload. The OCVRs are designed to deliver up to the average power requirement of the typical workloads executed on a CMP platform. The power demand of a core cluster exceeding the average value is delivered by combining the output of multiple OCVRs through a high-speed switch network. Different OCVR topologies are also being analyzed to understand the impact on voltage regulator characteristics as the peak load current is reduced. The run-time OCVR clustering concept is also being extended for application to many-core systems by solving the energy efficiency optimization problem.

3-D Integrated Free-Space Optical Interconnect for Multi-Core Systems

State of the art microprocessors and SoCs experience a degradation in the performance and signal integrity of on-chip metal interconnects with each successive technology generation due to increased resistance and signal bandwidth demands. These systems have therefore become increasingly communications limited. We proposed a fully-distributed intra-chip interconnect based on free-space optics, 3-D integrated photonic devices, and 3-D integrated analog and digital device planes. The main motivation was to construct a communication network with a large bandwidth density and without switching nodes. This free-space optical interconnect (FSOI) system consists of a photonics layer and a free-space optical guiding medium constructed using micro-mirrors and micro-lenses, which are stacked on top of two CMOS electronics layer by 3-D chip integration. The light source generated by an electrically modulated vertical-cavity surface emitting laser (VCSEL) is focused by a microlens at the backside of the GaAs substrate. After bouncing from the mirrors on the package multiple times, it is focused by another micro-lens onto a photodetector (PD), where it is converted back into an electrical signal and then processed by the CMOS transceiver located directly below the PD and connected through TSVs. This multi-technology project merging photonics devices with traditional CMOS technology is but a single example of the system level complexity that can be achieved with 3-D integrated circuits.

Thermal Modeling and Mitigation

Two of the most omnipresent and challenging issues in high performance 3-D systems are power delivery and thermal management. The interdependence of these issues is of critical importance to 3-D systems, as noise on the power network can produce severe hot spots within a 3-D stack. Enhanced understanding of these interrelated 3-D design challenges is therefore necessary to develop design techniques and methodologies to effectively deliver power while managing thermal effects. Thermal effects can potentially alter the performance of the clock and power networks due to hot spots. A test circuit has been fabricated by Tezzaron Semiconductor in a 130 nm CMOS technology with 1.2 micrometers. A face-to-face bonding technique to vertically stack two logic device planes has been implemented by Tezzaron. Test structures have been developed to evaluate thermal coupling within 3-D systems. This test circuit is designed to better understand the effects of inter- and intra-plane thermal resistances on hot spot formation. We have also examined the thermal impact that bundled VCSELs have in a 3-D stack, as the top surface usually utilized by a heat sink is now occupied by photonic devices. Thermal models of the two-tiered CMOS planes were developed in Hot Spot to compare with the experimental results, and to explore mitigation techniques of thermal hot spots.